A ASML planeia aplicar amplamente a tecnologia High‑NA EUV já no próximo ano para fabricar chips com tamanho de transistor de 1,4 nm ou menos.

Resumo

A nova fase de miniaturização de circuitos requer a adoção de métodos avançados de litografia. Nos próximos dois anos, o setor deve iniciar a produção de chips usando equipamentos de classe High‑NA EUV, que permitem atingir tamanhos até 8 nm em uma única passagem e abrem caminho para processos de 1,4 nm e menos de 10 nm (DRAM).

1. Capacidades tecnológicas do High‑NA EUV

Parâmetro | Valor

Abertura numérica (NA) | 0,55

Tamanho mínimo por passagem | ≤ 8 nm

Processos potenciais | 1,4 nm (circuitos integrados), < 10 nm (DRAM)

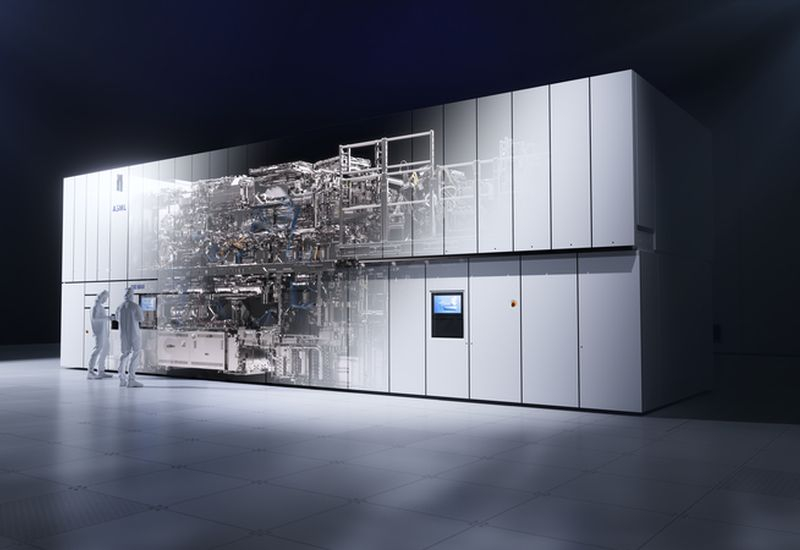

Essas características tornam os equipamentos ASML Twinscan EXE:5200B e soluções semelhantes críticos para as futuras tecnologias de microeletrônica.

2. Principais players

Empresa | Status de implementação | Comentário

ASML | Fabricante High‑NA EUV | Primeiros clientes: Intel, Samsung, SK Hynix; TSMC não pronto para uso em massa. Custo de um sistema – 380 milhões USD; plano de abandonar chips de 1,4 nm.

Intel | Em dezembro de 2023 introduziu o Twinscan EXE:5200B | Preparação para lançamento da tecnologia 14A e equipamentos associados.

Samsung Electronics | Recebeu o primeiro scanner em dezembro de 2023; segundo neste semestre | Planeja usá‑lo no Exynos 2600 (2 nm) e futuros processadores Tesla.

SK Hynix | Adota High‑NA EUV desde setembro de 2023 | Já usa litografia EUV padrão em DRAM (10 nm), planeja usar pelo menos cinco camadas EUV para a sexta geração.

Micron Technology | Ainda não definiu prazos de implementação | Possíveis planos com High‑NA EUV.

Rapidus (Japão) | Adota tecnologia de 2 nm; planeja 1,4 nm em 2029 | Em 2027 deve iniciar produção em massa de chips de 2 nm no Hokkaido.

3. Aspectos econômicos

* Custo do equipamento – um sistema High‑NA EUV custa cerca de 380 milhões USD.

* A migração para equipamentos mais caros aumenta o custo de produção, refletindo-se nos consumidores finais.

* Por isso, grandes fabricantes (TSMC, Rapidus) adotam cautela e planejam a implementação em etapas.

4. Prazos esperados

Os novos scanners litográficos ASML para produção em massa de semicondutores avançados começarão a ser usados ativamente entre 2027 e 2028. Até lá, as empresas ajustarão gradualmente suas linhas de produção, integrando High‑NA EUV nos processos tecnológicos existentes.

Conclusão

A transição para High‑NA EUV é um passo chave para alcançar tamanhos até 1,4 nm e DRAM mais compactos. Os maiores players globais já iniciaram preparações, mas a adoção em massa só ocorrerá nos próximos anos devido aos altos custos e à necessidade de adaptar as cadeias de produção.

Asted Cloud

Asted Cloud

Comentários (0)

Compartilhe sua opinião — por favor, seja educado e mantenha-se no tema.

Faça login para comentar